## Test n°2 du 2 décembre 2005

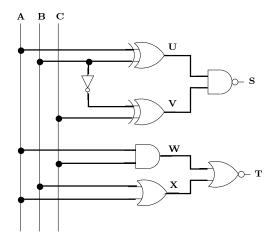

Exercice 1. Écrire les tables de vérités des fonctions Booléennes U, V, W, X, S et T décrites par le circuit ci-dessous :

**Exercice 2.** On souhaite réaliser un circuit possèdant 3 entrées A, B et C et une sortie S. La sortie S vaut 1 si

$$-C = 1 \text{ et } B = 0.$$

$-C = 0, A = 1 \text{ et } B = 0.$

- (1) Ecrire les diagrammes de Karnaugh de S et  $\overline{S}$ .

- (2) Etablir deux expressions Booléennes réalisant S et  $\overline{S}$ .

- (3) Dessiner un circuit réalisant S en précisant le nombre de portes utilisées.

## Exercice 3.

- (1) Dessiner le circuit du semi-additionneur 1 bit en précisant les expressions Booléennes des sorties.

- (2) Comment réaliser un additionneur 1 bit complet à partir de deux semi-additionneurs 1-bits?

(3) Comment réaliser un additionneur 4 bits à partir d'additionneur 1 bit complet?

## Exercice 4 (Représentation des entiers).

- (1) Donner la représentation binaire sur 8 bits de 25 et −25 en utilisant la représentation en complément à 2. Comment passe-t-on de la representation d'un entier à celle de son opposé?

- (2) A quels entiers relatifs correspondent les représentations 10010111 et 01101000 sur 8 bits en complément à 2?

- (3) Effectuez les opérations suivantes avec une représentation des entiers relatifs en compléments à deux sur 8 bits :

Note. On précisera les retenues effectuées.

Indiquer si les résultats ont un sens avec des entiers relatifs codés sur 8 bits. Comment détecter si le résultat d'une addition doit être prise en compte ou pas?

(4) Quels entiers relatifs représente-t-on en complément à deux sur 64 bits?

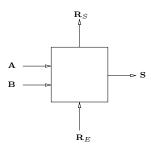

Exercice 5 (Comparateur 1 bit - Comparateur 2 bits). L'objectif est de réaliser un circuit prenant en entrées deux mots A et B de n bits représentant un entier naturel codé en binaire et trois sorties S, I et E prenant les valeurs 1, 0, 0 si l'entier A est strictement inférieur à B, 0, 1, 0 si l'entier A est strictement inférieur à B et 0, 0, 1 si les deux entiers A et B sont égaux.

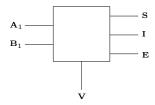

Comparateur 1-bit: Dans un premier temps, on réalise un comparateur élémentaire de deux mots de 1 bits  $A_1$  et  $B_1$  activé ou désactivé par un bit V:

Fig. 1. Comparateur 1-bit

Si V vaut 1 les trois sorties S, I et E sont mises à 0 alors que si V=0, le comparateur 1-bit compare  $A_1$  et  $B_1$  et renvoie

- $-S = 1, I = 0, E = 0 \text{ si } A_1 > B_1.$

- $-S = 0, I = 1, E = 0 \text{ si } A_1 < B_1.$

- $-S = 0, I = 0, E = 1 \text{ si } A_1 = B_1.$

- (1) Ecrire les diagrammes de Karnaugh des trois sorties S, I et E.

- (2) Etablir les expressions booléennes de S, I et E en utilisant exclusivement les opérateurs  $+, \cdot$  et -

- (3) Dessiner un circuit implémentant les expressions Booléennes de  $S,\,I$  et E en précisant le nombre de portes logiques utilisées.

Note. On pourra utiliser l'ensemble des portes logiques et on précisera l'expression implantée. Les portes utilisées ne devront comporter que deux entrées.

Comparateur 2-bit: On souhaite maintenant étendre le comparateur à deux mots de 2 bits  $A_2A_1$  et  $B_2B_1$ . On convient que :

$$A_2A_1 > B_2B_1$$

si et seulement si  $A_2 > B_2$  ou  $\left(A_2 = B_2 \text{ et } A_1 > B_1\right)$

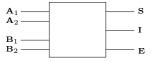

En utilisant deux copies du comparateur 1-bit et des portes logiques (ET, OU, NON, NON-ET, NON-OU, OU-EXCLUSIF), réaliser le circuit ci-dessous :